#### AIUTI A SOSTEGNO DEI CLUSTER TECNOLOGICI REGIONALI PER L'INNOVAZIONE

**PERSON** - PERVASIVE GAME FOR PERSONALIZED TREATMENT OF COGNITIVE AND FUNCTIONAL DEFICITS ASSOCIATED WITH CHRONIC AND NEURODEGENERATIVE DESEASES.

# Deliverable D10.4 – Progettazione del set-up di calcolo FPGA based e degli algoritmi programmazione FPGA e valutazioni comparative fra gli approcci usati

Codice Progetto : LQ8FBY0

Titolo Progetto : PERSON

Numero Deliverable : D10.4

Titolo Deliverable : Progettazione del set-up di calcolo FPGA based e degli

algoritmi programmazione FPGA e valutazioni comparative

fra gli approcci usati

Natura del Deliverable : Report

Mese di Rilascio da Capitolato : Luglio 2017

Livello di Disseminazione : Pubblico

Versione : 1.0

Data Deliverable : 4/8/2017

#### Abstract

Dopo aver individuato la piattaforma di calcolo FPGA, vengono descritte le fasi di progettazione ed implementazione del set-up di calcolo. Si spiega quindi il pacchetto software realizzato per interfacciarsi con il modulo hardware.

Infine si confrontano le prestazioni del SDVA con scheda FPGA e quelle del SDVA basato su GPU.

## **Keyword list**

FPGA, frame grabber, elaborazioni di immagini, prestazioni di elaborazione

## Tracking delle Versioni

| Version | Changes     | Author(s)                                |

|---------|-------------|------------------------------------------|

| 1.0     | First Draft | Maria Francesca de Ruvo, Marco Colaprico |

\_\_\_\_\_

# Indice

| ABSTRACT                                                                                                                                                                | 2  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| KEYWORD LIST                                                                                                                                                            | 2  |

| INDICE                                                                                                                                                                  | 3  |

| INDICE FIGURE                                                                                                                                                           | 5  |

| INDICE GRAFICI                                                                                                                                                          | 5  |

| INDICE TABELLE                                                                                                                                                          | 6  |

| GLOSSARIO, ACRONIMI E ABBREVIAZIONI                                                                                                                                     |    |

| 1. INDIVIDUAZIONE DELLA PIATTAFORMA DI CALCOLO FPGA                                                                                                                     | 8  |

| 1.1 BANDA RICHIESTA DAL SET-UP DI VISIONE ARTIFICIALE                                                                                                                   |    |

| 1.2 CONFRONTO TRA GLI STANDARD HARDWARE DI VISIONE                                                                                                                      | 8  |

| 1.2.1 Camera Link                                                                                                                                                       |    |

| 1.2.2 Camera Link HS                                                                                                                                                    | _  |

| 1.2.3 CoaXPress                                                                                                                                                         |    |

| 1.2.4 GigE Vision                                                                                                                                                       |    |

| 1.2.5 USB3                                                                                                                                                              |    |

| 1.2.6 Scelta dello standard                                                                                                                                             |    |

| 1.3 SCELTA DEL FRAME GRABBER CON SCHEDA FPGA A BORDO                                                                                                                    | 10 |

| 2. OTTIMIZZAZIONE DI ALGORITMI DI ANALISI TESI ALLA RICOSTRUZIONE 3D DELLA GESTUALIT<br>MOTO DEL PLAYER DEL SERIOUS GAMES, PARTENDO DA UN FLUSSO VIDEO STEREO @50FPS, F |    |

| VENGANO MAPPATI IN HARDWARE                                                                                                                                             | 12 |

| 2.1 COMPONENTI HARDWARE DELL'SDVA                                                                                                                                       | 13 |

| 2.1.1 Markers                                                                                                                                                           | 13 |

| 2.1.2 Illuminatori                                                                                                                                                      |    |

| 2.1.3 Filtri                                                                                                                                                            | 13 |

| 3. PROGETTAZIONE DI UN SET UP DI CALCOLO BASATO SU HARDWARE CONFIGURABILE                                                                                               |    |

| 3.1 Architettura del Sistema Di Visione Artificiale                                                                                                                     |    |

| 3.2 FLOW CHART CONCETTUALE DELL'ALGORITMO DI VISIONE                                                                                                                    | 15 |

| 4. IMPLEMENTAZIONE DEL SET UP INDIVIDUATO NEL CAPITOLO 3 SULLA PIATTAFORMA INDIV                                                                                        |    |

| NEL CAPITOLO 1                                                                                                                                                          |    |

| 4.1 MAPPATURA HARDWARE DELL'ALGORITMO DI VISIONE                                                                                                                        |    |

| 4.2 TEST E DEBUG DEL MODULO FPGA EMBEDDED                                                                                                                               |    |

| 4.3 SINTESI E DOWNLOAD                                                                                                                                                  |    |

| 5. INTEGRAZIONE DEL MODULO IMPLEMENTATO CON IL SET UP DI VISIONE ARTIFICIALE                                                                                            |    |

| 5.1 SINCRONIZZAZIONE DELLE TELECAMERE                                                                                                                                   |    |

| 5.1.1 Modulo Hardware                                                                                                                                                   |    |

| 5.1.2 Impostazioni software                                                                                                                                             |    |

| 5.1.3 Valutazioni sul modulo di sincronizzazione implementato                                                                                                           |    |

| 5.2 Interfaccia Software                                                                                                                                                |    |

| 5.2.2 Modulo di processing                                                                                                                                              |    |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                   |    |

| 6 TEST E DEBUG DEL SISTEMA INTEGRATO                                                                                                                                    |    |

| 6.1 Problema dell'instabilità del puntamento                                                                                                                            | 29 |

| 6.2 SOLUZIONE ALL'INSTABILITÀ DEL PUNTAMENTO                           | 32         |

|------------------------------------------------------------------------|------------|

| 6.3 VALUTAZIONE PRESTAZIONI                                            | 35         |

| 7 APPLET PERSON1.6                                                     | 37         |

| 7.1 CARATTERISTICHE                                                    | 37         |

| 7.2 Parametri                                                          | 37         |

| 7.3 Banda                                                              | 38         |

| 7.4 Requisiti                                                          | 38         |

| 7.4.1 Requisiti Software                                               | 39         |

| 7.4.2 Requisiti Hardware                                               | 39         |

| 7.4.3 Licenza                                                          | 39         |

| 7.5 Interfaccia delle telecamere                                       |            |

| 7.6 Trasferimento delle immagini e dei dati alla memoria del PC        | 39         |

| 8 GBECAMERASDK                                                         | <b>3</b> 9 |

| 8.1 Struttura                                                          | 39         |

| 8.2 Requisiti                                                          | 40         |

| 8.3 Interfaccia delle telecamere                                       | 40         |

| APPENDICE 1 – STRUTTURA DEL LOG DEL MODULO DI PROCESSING               | 40         |

| APPENDICE 2 – STRUTTURA DEL LOG DEL MODULO DI ACQUISIZIONE             | 41         |

| APPENDICE 3 – STRUTTURA DEL LOG DEL TEST DI INSTABILITÀ DEL PUNTAMENTO | 42         |

| ALLEGATI DEL MODULO HARDWARE                                           | 43         |

| ALLEGATI DEL PACCHETTO SOFTWARE                                        | 43         |

| ALLEGATI LOG MODULO PROCESSING                                         | 43         |

| ALLEGATI LOG MODULO ACQUISIZIONE                                       | 43         |

| ALLEGATI LOG TEST DELL'INSTABILITÀ DEL PUNTAMENTO                      | 44         |

| BIBLIOGRAFIA                                                           | 44         |

# Indice figure

| FIGURA 1. SCHEMATIZZAZIONE DELLA CONFIGURAZIONE PROTOTIPALE DEL SISTEMA PERSON, IN CUI IL GAME SARÀ FRUITO SU UN NI                                                                                                                               |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| SCHERMO LCD.                                                                                                                                                                                                                                      |             |

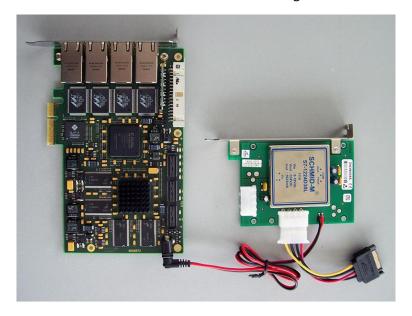

| FIGURA 2. MEIV VQ4-GPOE CONNESSO AL MODULO DI ALIMENTAZIONE.                                                                                                                                                                                      |             |

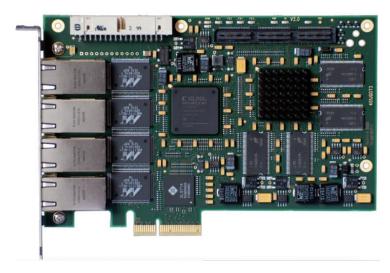

| FIGURA 3. VIDEO PROCESSOR MEIV-VQ4GE DELLA SILICON SOFTWARE.                                                                                                                                                                                      |             |

| FIGURA 4. MARCATORE PASSIVO DOTATO DI RIVESTIMENTO RIFLETTENTE 3M 7610 E FILETTATURA INTERNA PER IL FISSAGGIO                                                                                                                                     |             |

| Figura 5. OverDrive Ring Light 850nm IR - EZ Mount Ring Light                                                                                                                                                                                     |             |

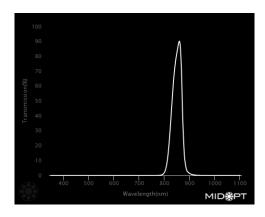

| Figura 6. Caratteristica "Trasmissione=f( $\lambda$ )" del filtro BN850-27                                                                                                                                                                        |             |

| Figura 7. Architettura del SDVA (Sensore Di Visione Artificiale).                                                                                                                                                                                 | 15          |

| FIGURA 8. FLOW CHART CONCETTUALE DELL'ALGORITMO DI VISIONE.                                                                                                                                                                                       |             |

| Figura 9. Diagramma a blocchi del flusso di lavoro                                                                                                                                                                                                |             |

| Figura 10. Telecamera JAI GO-5000-PGE                                                                                                                                                                                                             |             |

| FIGURA 11. PROGETTO VISUAL APPLET DELL'ALGORITMO DI VISIONE RELATIVO AL PROCESSO 0                                                                                                                                                                |             |

| Figura 12. Disegno relativo al blocco Merge del Processo 0.                                                                                                                                                                                       |             |

| FIGURA 13. RISORSE FPGA UTILIZZATE DALL'ALGORITMO DI VISIONE                                                                                                                                                                                      |             |

| FIGURA 14. IMMAGINE BINARIA UTILIZZATA PER IL TEST FUNZIONALE DELL'APPLET                                                                                                                                                                         | 21          |

| FIGURA 15. RISULTATI DELL'ANALISI DEI BLOB. È POSSIBILE LEGGERE IL CENTRO DI MASSA, L'AREA E IL BYTE RELATIVO AGLI ERRORI                                                                                                                         |             |

| DELL'ANALISI, DELLE PRIME TRE REGIONI DELL'IMMAGINE IN FIGURA 13                                                                                                                                                                                  | 21          |

| FIGURA 16 RISULTATO DELL'ANALISI DI BANDA DELL'APPLET PERSON1.3 OTTENUTO IMPOSTANDO COME ROI LA DIMENSIONE MASSI<br>FRAME 2560*2048                                                                                                               |             |

| Figura 17 Diagramma della parte esterna del circuito di ingresso                                                                                                                                                                                  |             |

| Figura 18 Diagramma della parte esterna del circuito di uscita                                                                                                                                                                                    |             |

| Figura 19 Vista dall'esterno del connettore Hirose a 6 pin e tabella dell'assegnamento dei pin                                                                                                                                                    |             |

| FIGURA 20 CIRCUITO PER LA SINCRONIZZAZIONE DELLE TELECAMERE                                                                                                                                                                                       |             |

| FIGURA 21 COMPONENTI DEL SISTEMA DI VISIONE ARTIFICIALE                                                                                                                                                                                           |             |

| Figura 22 Diagramma delle classi di GBEStereo                                                                                                                                                                                                     |             |

| Figura 23 Diagramma delle classi di Gdesterlo                                                                                                                                                                                                     |             |

| Figura 24 Disegno relativo al blocco calculate_normalized_CoG                                                                                                                                                                                     |             |

| Figura 25 Progetto Visual Applet dell'algoritmo di visione relativo al Processo 0                                                                                                                                                                 |             |

| Figura 26 Risorse FPGA utilizzate dall'applet Person1.6                                                                                                                                                                                           |             |

| FIGURA 27 CONFRONTO DEI TEMPI DI ELABORAZIONE                                                                                                                                                                                                     |             |

| Figura 28 Interfaccia delle telecamere e Setup dei Cavi                                                                                                                                                                                           |             |

| FIGURA 29 INTERFACCIA DELLE TELECAMERE E SETUP DEI CAVI                                                                                                                                                                                           |             |

| Indice grafici                                                                                                                                                                                                                                    |             |

| GRAFICO 1 DIFFERENZA TRA L'ISTANTE DI ACQUISIZIONE DELLA TELECAMERA MASTER E DELLA SLAVE                                                                                                                                                          | 25          |

| GRAFICO 2 GRAFICO DELLA COORDINATA X DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO                                                                                                                                 | 23          |

| DALL'UTENTE RIMANE COSTANTE PER 24 SECONDI                                                                                                                                                                                                        | 30          |

| GRAFICO 3 GRAFICO DELLA COORDINATA Y DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO DA                                                                                                                              | ALL'UTENTE  |

| RIMANE COSTANTE PER 24 SECONDI                                                                                                                                                                                                                    | 50          |

| GRAFICO 4 GRAFICO DELLA COORDINATA X DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO  DALL'UTENTE RIMANE COSTANTE PER 24 SECONDI. RELATIVO AL TRONCAMENTO DEI CENTRI DI MASSA DEI MARKERS RISPETTIV.                 |             |

| 0, 1, 2, 3 e 6 CIFRE DECIMALI                                                                                                                                                                                                                     |             |

| GRAFICO 5 GRAFICO DELLA COORDINATA Y DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO DA RIMANE COSTANTE PER 24 SECONDI. RELATIVO AL TRONCAMENTO DEI CENTRI DI MASSA DEI MARKERS RISPETTIVAMENTE A 0, CIFRE DECIMALI. | 1, 2, 3 E 6 |

| GRAFICO 6 GRAFICO DELLA COORDINATA X DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO                                                                                                                                 |             |

| DALL'UTENTE RIMANE COSTANTE PER 24 SECONDI. RELATIVO AL TRONCAMENTO A 0 CIFRE DECIMALI DEI CENTRI DI MASSA DEI                                                                                                                                    |             |

| GRAFICO 7 GRAFICO DELLA COORDINATA Y DEL PIXEL SELEZIONATO DAL SDVA AL VARIARE DEL TEMPO, MENTRE IL PIXEL PUNTATO DA                                                                                                                              |             |

| RIMANE COSTANTE PER 24 SECONDI. RELATIVO AL TRONCAMENTO A O CIERE DECIMALI DEI CENTRI DI MASSA DEI MARKERS                                                                                                                                        |             |

| GRAFICO 8 TEMPI DI ELABORAZIONE DELLA CPU DEL SDVA CON FRAME GRABBER                                                   |         |

|------------------------------------------------------------------------------------------------------------------------|---------|

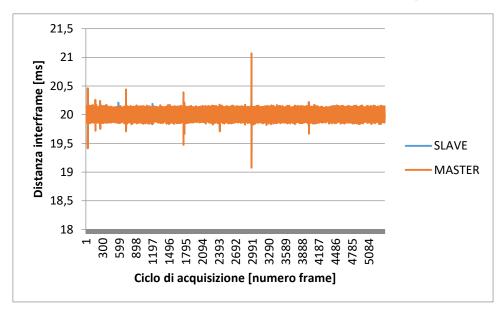

| GRAFICO 9 DISTANZA INTERFRAME DEL SDVA CON FRAME GRABBER, NEL CASO DI FRAME RATE DI 50FPS                              | 36      |

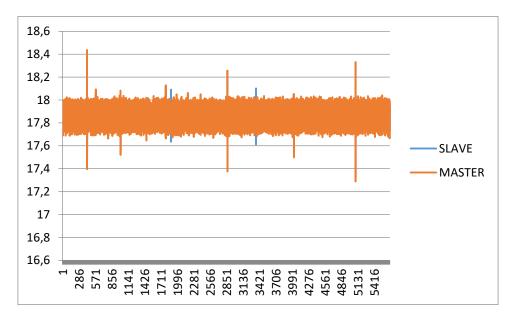

| GRAFICO 10 DISTANZA INTERFRAME DEL SDVA CON FRAME GRABBER, NEL CASO DI FRAME RATE DI 56FPS                             | 37      |

| Indice tabelle                                                                                                         |         |

| TABELLA 1. CONFRONTO TRA GLI STANDARD HARDWARE DI VISIONE ARTIFICIALE. IN VERDE SONO EVIDENZIATE LE CARATTERISTICHE DE | -       |

| PROTOCOLLI CHE VERIFICANO LE SPECIFICHE DEL SET UP DI VISIONE PER LA RICOSTRUZIONE DELLA GESTUALITÀ DEL PAZIENTE       |         |

| TABELLA 2. CARATTERISTICHE DEL DISPOSITIVO MICROENABLE IV VQ4-GE.                                                      | 11      |

| TABELLA 3. SOMMARIO DEGLI ATTRIBUTI DEI DISPOSITIVI DELLA FAMIGLIA SPARTAN-3 FPGA. IN VERDE È EVIDENZIATO L'FPGA MONT  | ATO SUL |

| FRAME GRABBER MICROENABLE IV VQ4-GE                                                                                    | 12      |

| TABELLA 4. TABELLA SINTETICA DELL'UTILIZZO DELLE RISORSE DELL'FPGA                                                     | 19      |

| TABELLA 9 CONFIGURAZIONE DELLA TELECAMERA MASTER                                                                       | 24      |

| TABELLA 10 CONFIGURAZIONE DELLA TELECAMERA SLAVE                                                                       | 24      |

| TABELLA 11 TABELLA SINTETICA DELL'UTILIZZO DELLE RISORSE DELL'FPGA NEL PROGETTO CHE PREVEDE 6 DMA                      | 33      |

| TABELLA 12 TABELLA SINTETICA DELL'UTILIZZO DELLE RISORSE DELL'FPGA NEL PROGETTO CHE PREVEDE 4 DMA                      | 33      |

| TABELLA 13 TABELLA DEGLI INDICI DELLE RISORSE UTILIZZATE                                                               | 34      |

| TABELLA 5 SOMMARIO DELLE CARATTERISTICHE DELL'APPLET PERSON1.3                                                         | 37      |

| Tabella 6 Proprietà dei parametri del Process0                                                                         | 38      |

| TABELLA 7 PROPRIETÀ DEI PARAMETRI DEL PROCESS1                                                                         | 38      |

| TABELLA 8 BANDA DI PERSON1.3                                                                                           | 38      |

# Glossario, acronimi e abbreviazioni

| Item     | Descrizione                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDVA     | Set up di visione artificiale                                                                                                                                 |

| 3D       | Tridimensionale                                                                                                                                               |

| 2D       | Bidimensionale                                                                                                                                                |

| LED      | Light Emitting Diode                                                                                                                                          |

| IR       | Infrarosso                                                                                                                                                    |

| ROI      | Region Of Interest, cioè la regione di interesse rispetto all'intero frame                                                                                    |

| nm       | Nanometro (1 nm = $10^{-9}$ m)                                                                                                                                |

| ms       | Millisecondi (1ms = 10 <sup>-3</sup> secondi)                                                                                                                 |

| GigE     | Standard hardware di visione Giga Ethernet Vision                                                                                                             |

| HS       | High Speed                                                                                                                                                    |

| USB      | Universal Serial Bus                                                                                                                                          |

| PoCL     | Power over Camera Link                                                                                                                                        |

| PoE      | Power over Ethernet                                                                                                                                           |

| fps      | Frame per second, cioè fotogrammi al secondo                                                                                                                  |

| Mpixel   | Megapixel                                                                                                                                                     |

| λ        | Lunghezza d'onda                                                                                                                                              |

| FPGA     | Field Programmable Gate Array, è un circuito integrato le cui funzionalità sono programmabili via software                                                    |

| Gbits/s  | Giga bits al secondo                                                                                                                                          |

| MB/s     | Mega bytes al secondo                                                                                                                                         |

| MHz      | Mega Hertz                                                                                                                                                    |

| GPU      | Graphical Processing Unit                                                                                                                                     |

| CPU      | Central Processing Unit                                                                                                                                       |

| PCle     | Peripheral Component Interconnect Express, standard di interfaccia d'espansione a bus seriale per computer usato per connettere periferiche alla scheda madre |

| DMA      | Direct Memory Access                                                                                                                                          |

| MEIV     | microEnable IV                                                                                                                                                |

| RAM      | Random Access Memory                                                                                                                                          |

| М        | Master                                                                                                                                                        |

| S        | Slave                                                                                                                                                         |

| DC       | Direct Current                                                                                                                                                |

| GPI      | General Purpose Input/Output                                                                                                                                  |

| Hirose 6 | Connettore Hirose a 6 pin                                                                                                                                     |

#### 1. Individuazione della piattaforma di calcolo FPGA

La necessità di elaborare immagini sempre più grandi e a frequenze sempre più elevate, ha portato alla richiesta di performances sempre più proibitive dei sistemi host. A questa esigenza il mercato della visione ha risposto con l'introduzione di frame grabber che montano a bordo un FPGA, consentendo di ridurre il carico di lavoro sull'host, scaricando le operazioni di image processing ripetitive ed intensive sulla scheda FPGA e liberando così risorse di calcolo preziose per il resto dell'applicazione con un conseguente miglioramento delle performances. Le operazioni candidate ad essere eseguite sulla piattaforma FPGA includono il filtraggio spaziale e temporale, il guadagno e la correzione dell'offset, la correzione dei pixel morti, la correzione della distorsione ottica e della prospettiva, le conversioni spazio colore e le trasformazioni nel dominio della frequenza.

La scelta della piattaforma di calcolo FPGA, verrà effettuata tra quelle montate sui frame grabber disponibili sul mercato, in modo tale da avere un'unica scheda hardware che effettua sia l'acquisizione che una parte dell'elaborazione a bordo dell'FPGA.

Prima di effettuare la scelta dell'FPGA è quindi necessario scegliere il protocollo di visione del frame grabber. Tale scelta verrà effettuata tra gli standard hardware in uso nell'industria della visione, alla luce delle specifiche di banda richieste del set up dell'SDVA.

#### 1.1 Banda richiesta dal Set-up di visione artificiale

Il set up di visione artificiale per la ricostruzione della gestualità del paziente, deve determinare in tempo reale e al troughput di 50 rilevazioni al secondo, quale è il pixel che il player sta indicando con la propria mano su uno schermo di tipo convenzionale (Figura 1), e fornire al sensor hub le coordinate di detto pixel, per permettere alle altre componenti del game una fluida interazione con il player.

Dato il volume oggetto dell'osservazione, inferiore ad 1 m³, si ritiene che telecamere con sensore di almeno 2-Mpixel (1920x1080) garantiscano una risoluzione adeguata. Esse dovranno avere compattezza, appropriata sensitività, oltre che consentire un frame rate di almeno 50 fps.

Il set-up di visione appena stabilito richiede una banda minima di 1Gigabit/s (1920x1080x8x50).

Figura 1. Schematizzazione della configurazione prototipale del sistema PERSON, in cui il game sarà fruito su un normale schermo LCD.

#### 1.2 Confronto tra gli standard hardware di visione

Gli standard hardware, in uso nell'industria della visione artificiale, che garantiscono alte prestazioni, sono i seguenti (1):

- CameraLink

- CameraLinkHS

- CoaXPress

- GigE Vision

- USB3 Vision

#### 1.2.1 Camera Link

Lo standard Camera Link è stato inizialmente rilasciato nel 2000. È un protocollo di comunicazione che standardizza la connessione tra la telecamera e il frame grabber e definisce un' interfaccia completa che comprende il trasferimento dei dati, il clock ed una segnalazione real time alla telecamera. Si tratta di un protocollo di comunicazione seriale ideato per le comunicazioni ad alta velocità, che garantisce una banda di 2.04Gbits/s nella modalità Base (un solo cavo) e 6.8Gbits/s nella modalità Full (due cavi). La lunghezza del cavo può essere al massimo di 10m. Inoltre una telecamera PoCL può essere alimentata mediante un frame grabber PoCL e un cavo Camera Link.

#### 1.2.2 Camera Link HS

Lo standard Camera Link HS è stato rilasciato nel maggio 2012 per migliorare quello Camera Link utilizzando dei cavi di rame e ottici per estendere la portata e migliorare la banda. Garantisce una banda di 3.125Gbits/s per linea con il protocollo M (cavi di rame) e 10.3Gbits/s con il protocollo X (cavi ottici). La massima lunghezza dei cavi di rame può arrivare a 15m, mentre quella dei cavi ottici a 600m. Tale standard offre anche la possibilità di effettuare l'elaborazione parallelamente su più frame grabber. A differenza dello standard Camera Link non è possibile alimentare le telecamere direttamente dal frame grabber.

#### 1.2.3 CoaXPress

Lo standard CoaXPress (CXP) è stato rilasciato nel dicembre 2010. Esso fornisce un'interfaccia ad alta velocità tra la telecamera e il frame grabber e consente grandi lunghezze dei cavi. Nella forma più semplice questo standard utilizza un singolo cavo coassiale (CXP-1) per trasmettere i dati dalla telecamera al frame grabber fino a 1.25Gbits/s; contemporaneamente trasmette i dati di controllo e i triggers dal frame grabber alla telecamera a 20.8 Mbits/s; e fonisce fino a 13W di potenza alla telecamera. Quando sono necessarie velocità più alte si ricorre all'aggregazione dei link che consente di arrivare a 6.25Gbits/s (CXP-6). Alla velocità del link di 1.25Gbits/s (CXP-1), CoaXPress supporta cavi lunghi fino a 100m, mentre alla massima velocità 6.25Gbits/s (CXP-6) si possono utilizzare cavi lunghi al massino 35mm con un diametro di 6mm.

#### 1.2.4 GigE Vision

GigE Vision è uno standard ampiamente utilizzato ed è stato sviluppato sfruttando il protocollo di comunicazione Ethernet (IEEE 802.3). È stato rilasciato nel maggio 2006 e rivisto nel 2010 (versione 1.2) e nel 2011 (versione 2.0). GigE Vision supporta più canali di stream e consente il trasferimento dell'immagine senza errori su distanze fino a 100m mediante cavi standard Ethernet e fino a 5Km su fibra ottica. Attualmente sono già disponibili sistemi che garantiscono una banda di 1 e 2 Gbits/s (usando 2 cavi) e stanno entrando nel mercato sistemi con una banda di 10Gbits/s. Con questo protocollo non è necessario utilizzare un frame grabber per l'acquisizione. Se si utilizza una scheda di rete o un frame grabber PoE è possibile alimentare le telecamere direttamente tramite cavo Ethernet.

#### 1.2.5 USB3

Lo standard USB3 è stato introdotto a fine 2011 e una nuova versione è stata pubblicata nel gennaio 2013. L'interfaccia USB porta ad una installazione plug and play, ad alti livelli di performances (fino a 400Mbytes/s) e alla possibilità di trasferire direttamente le immagini dalla telecamera alla memoria del PC senza necessariamente utilizzare un frame grabber. La massima lunghezza dei cavi standard USB può arrivare a 5m.

#### 1.2.6 Scelta dello standard

Tutti e cinque gli standard considerati garantiscono la banda di 1Gbits/s richiesta dal set-up di visione artificiale presentato nel primo paragrafo di questo capitolo. Ma dal confronto delle caratteristiche dei vari protocolli si è scelto di optare per lo standard GigE Vision perché sul mercato ci sono numerose telecamere che utilizzano tale standard, non necessita di un frame grabber e quindi consente di effettuare una comparazione tra gli algoritmi di visione sviluppati per FPGA e quelli per GPU, a differenza dello standard USB3 e del CameraLink consente una maggiore connettività dato che la massima lunghezza dei cavi può arrivare a 100m e, se si utilizza un frame grabber o una scheda di rete PoE, è possibile alimentare la telecamera direttamente dal cavo di rete in moda da semplificare il cablaggio e la complessità del sistema.

| Standard      | CAMERALINIC | Link HS"          | CoalPress   | GIG=          | USB°     |

|---------------|-------------|-------------------|-------------|---------------|----------|

| Banda         | Base Mode:  | M protocol        | CXP-1:      | Un solo cavo: | 5Gbits/s |

|               | 2.04Gbits/s | (cavo di rame):   | 1.25Gbits/s | 1Gbits/s      |          |

|               |             | 3.125Gbits/s      |             |               |          |

|               | Full Mode:  | X protocol (fibra | CXP-6:      | Due cavi:     |          |

|               | 6.8Gbits/s  | ottica):          | 6.26Gbits/s | 2Gbits/s      |          |

|               |             | 10.3Gbits/s       |             |               |          |

| Lunghezza     | 10 m        | Cavo di rame:     | CXP-1:      | 100m          | 5m       |

| massima dei   | assima dei  |                   | 100m        |               |          |

| cavi          |             | Fibra ottica:     | CXP-6:      |               |          |

|               |             | 500m              | 35m         |               |          |

| Alimentazione | Opzionale   | No                | Sì          | Sì Opzionale  |          |

| sul cavo      |             |                   |             |               |          |

| Necessità del | Sì          | Sì                | Sì Sì       |               | No       |

| frame grabber |             |                   |             |               |          |

Tabella 1. Confronto tra gli standard hardware di visione artificiale. In verde sono evidenziate le caratteristiche dei protocolli che verificano le specifiche del set up di visione per la ricostruzione della gestualità del paziente.

#### 1.3 Scelta del frame grabber con scheda FPGA a bordo

GigE Vision si è rivelato essere lo standard più appropriato al set-up di visione scelto. La scelta della piattaforma di calcolo è quindi limitata ai frame grabbers GigE Vision che montano a bordo un FPGA.

Un studio di mercato ha rivelato che la maggior parte dei produttori di video processor realizzano frame grabber con a bordo schede FPGA solo per gli standard CameraLink e CoaXPress (2) (3) (4). Mentre Silicon Software (5) realizza frame grabbers dotati di scheda FPGA per quasi tutti gli standard analizzati (CameraLink, CameraLinkHS, CoaXPress, GigE Vision). Per gli standard CameraLink e CoaxPress, la Silicon Software mette a disposizione la possibilità di poter scegliere tra più serie di prodotti (microEnable 5 ironman (6) che monta a bordo uno Xilinx FPGA Virtex 6 series, microEnable 5 marathon (7) che monta a bordo uno Xilinx FPGA of Kintex 7 series, LightBridge (8) e microEnable IV (9)). Per lo standard GigE Vision è disponibile sono la serie microEnable IV (9) e in particolare sono disponibili 4 prodotti:

- 1. microEnable IV AQ4-GE (10)

- 2. microEnable IV AQ4-GPoE (11)

- 3. microEnable IV VQ4-GE (12)

- 4. microEnable IV VQ4-GPoE (13)

I primi 2 dispositivi elencati appartengono alla serie dei frame grabber non programmabili (A series) e vanno quindi scartati, mentre gli ultimi 2 fanno parte della serie programmabile (V series). La Silicon Software per la programmazione dell'FPGA mette a disposizione un ambiente di sviluppo grafico (Visual Applet) che rende semplice l'implementazione di algoritmi di elaborazione dell'immagine e che può essere utile per ridurre i tempi di sviluppo.

Gli ultimi due dispositivi dell'elenco differiscono solo per la capacità di supportare delle telecamere Power over Ethernet (PoE). Il frame grabber microEnable IV VQ4-GPoE però, per il corretto funzionamento necessita un ulteriore modulo di alimentazione, come è possibile notare in **Errore. L'origine riferimento non è stata trovata.**. Per evitare di montare sul pc anche il modulo di alimentazione, si può utilizzare il frame grabber microEnable IV VQ4-GE e alimentare le telecamere GigE mediante il cavo di alimentazione.

Figura 2. MEIV VQ4-GPoE connesso al modulo di alimentazione.

Le caratteristiche del frame grabber microEnable IV VQ4-GE sono elencate nella Tabella 2. Come di può notare il frame grabber consente l'interfacciamento con quattro telecamere GigE, ciò può risultare utile per una possibile futura espansione dall'attuale configurazione ad un set up che comprenda 2 coppie stereo.

| Caratteristiche del dispositivo                 |                                             |  |  |  |

|-------------------------------------------------|---------------------------------------------|--|--|--|

| Processore Vision Processor, Spartan3 FPGA XC3S |                                             |  |  |  |

| Memoria a bordo del dispositivo                 | 512 MByte DDR-RAM                           |  |  |  |

| Modulo di interfaccia I/O                       | Trigger/GPIO-IF (Opto Trigger, TTL Trigger) |  |  |  |

| Numero di Porte GigE                            | 4                                           |  |  |  |

| PC Bus Interface                                | PCI Express x4 (Gen1), DMA900               |  |  |  |

Tabella 2. Caratteristiche del dispositivo microEnable IV VQ4-GE.

Figura 3. Video processor MEIV-VQ4GE della Silicon Software.

Si può concludere che il frame grabber microEnable IV VQ4-GE della Silicon Software, verifica tutti i requisiti del set-up scelto per l'SDVA in quanto è basato sullo standard hardware:GigE Vision, ha un numero di porte GigE maggiore di due e monta a bordo come FPGA programmabile lo Spartan3 della Xilinx (14).

|             | System | Equivalent<br>Logic Cells <sup>(1)</sup> | CLB Array<br>(One CLB = Four Slices) |         | Distributed   | Block    | Dedicated            |             | Max. | Maximum  |           |

|-------------|--------|------------------------------------------|--------------------------------------|---------|---------------|----------|----------------------|-------------|------|----------|-----------|

|             | Gates  |                                          | Rows                                 | Columns | Total<br>CLBs | (K=1024) | RAM Bits<br>(K=1024) | Multipliers | DCMs | User I/O | I/O Pairs |

| XC3S50(2)   | 50K    | 1,728                                    | 16                                   | 12      | 192           | 12K      | 72K                  | 4           | 2    | 124      | 56        |

| XC3S200(2)  | 200K   | 4,320                                    | 24                                   | 20      | 480           | 30K      | 216K                 | 12          | 4    | 173      | 76        |

| XC3S400(2)  | 400K   | 8,064                                    | 32                                   | 28      | 896           | 56K      | 288K                 | 16          | 4    | 264      | 116       |

| XC3S1000(2) | 1M     | 17,280                                   | 48                                   | 40      | 1,920         | 120K     | 432K                 | 24          | 4    | 391      | 175       |

| XC3S1500    | 1.5M   | 29,952                                   | 64                                   | 52      | 3,328         | 208K     | 576K                 | 32          | 4    | 487      | 221       |

| XC3S2000    | 2M     | 46,080                                   | 80                                   | 64      | 5,120         | 320K     | 720K                 | 40          | 4    | 565      | 270       |

| XC3S4000    | 4M     | 62,208                                   | 96                                   | 72      | 6,912         | 432K     | 1,728K               | 96          | 4    | 633      | 300       |

| XC3S5000    | 5M     | 74,880                                   | 104                                  | 80      | 8,320         | 520K     | 1,872K               | 104         | 4    | 633      | 300       |

#### Notes:

- Logic Cell = 4-input Look-Up Table (LUT) plus a "D" flip-flop. "Equivalent Logic Cells" equals "Total CLBs" x 8 Logic Cells/CLB x 1.125 effectiveness.

- These devices are available in Xilinx Automotive versions as described in DS314: Spartan-3 Automotive XA FPGA Family.

Tabella 3. Sommario degli attributi dei dispositivi della famiglia Spartan-3 FPGA. In verde è evidenziato l'FPGA montato sul frame grabber microEnable IV VQ4-GE.

# 2. Ottimizzazione di algoritmi di analisi tesi alla ricostruzione 3D della gestualità o del moto del player del serious games, partendo da un flusso video stereo @50fps, perché essi vengano mappati in hardware

Il workflow che si è deciso di adottare per la ricostruzione 3D del moto del player del serious game è quello che fa uso di markers. Poiché tra le operazioni candidate ad essere eseguite sulla piattaforma FPGA, vi sono la sogliatura del frame e le operazioni di estrazione delle features degli oggetti segmentati (l'area, la bounding box, il centro di massa ecc) si è deciso di non utilizzare dei markers grafici, ma bensì dei markers di tipo spot (led attivi o riflettori passivi).

Per ridurre l'operazione di segmentazione dei markers ad una semplice sogliatura, è necessario aumentare il contrasto tra marcatore e sfondo. Per i sistemi passivi si possono utilizzare dei markers di materiale fortemente retroriflettente e una fonte di illuminazione collocata in modo solidale ad ogni telecamera. Per quelli attivi, si può far uso di marcatori LED impulsati in modo sincrono con lo shutter delle telecamere digitali. In entrambi i tipi di sistemi, per ridurre l'interferenza di sorgenti luminose terse, si possono dotare

le telecamere di filtri ottici centrati sulla lunghezza d'onda della sorgente di illuminazione (in caso di marker attivi) o di emissione (marker attivi) LED.

Una differenza significativa tra i sistemi è che i marcatori attivi possono essere identificati in modo univoco grazie alla modulazione dei loro impulsi, mentre i sistemi passivi devono dedurre l'identità del marker dall'osservazione continua di questi ultimi. Entrambi i tipi di sistemi ottici generano in modo affidabile la posizione esatta dei marcatori.

Nella fattispecie, consultandosi con il partner SENSICHIPS, responsabile della progettazione e realizzazione del guanto aptico, si è optato per marcatori passivi, piuttosto che per quelli attivi, per sgravare il guanto stesso da problematiche legate all'alimentazione dei LED.

#### 2.1 Componenti Hardware dell'SDVA

Alla luce delle precedenti considerazioni, il SDVA che si è deciso di realizzare sarà basato sulla componentistica di seguito descritta.

#### 2.1.1 Markers

Come detto si opterà per marcatori passivi, per non gravare il sensore aptico con problematiche legate all'alimentazione di marcatori attivi. Nello specifico, si sono scelti dei marcatori sferici rivestiti da Reflective Tape "3M 7610" del diametro di ¼ di pollice (6.4 mm), che consentono il fissaggio sul guanto aptico, attraverso opportune viti, grazie ad una predisposizione filettata, come visibile in Figura 4

Figura 4. Marcatore passivo dotato di rivestimento riflettente 3M 7610 e filettatura interna per il fissaggio.

#### 2.1.2 Illuminatori

Avendo optato per un approccio basato su marcatori passivi, è opportuno demandare l'illuminazione a sorgenti terze rispetto ai marcatori stessi, affinché essi siano comunque ben nitidi nelle immagini da elaborare.

Allo scopo di non creare disturbo al player e rendere il più neutro possibile il SDVA, si è considerata una lunghezza d'onda nella banda IR, e specificatamente quella ad 850 nm. Si è pertanto scelto di adoperare gli illuminatori ad anello "OverDrive Ring Light 850nm IR - EZ Mount Ring Light" della Smart Vision Light (Figura 5).

Figura 5. OverDrive Ring Light 850nm IR - EZ Mount Ring Light.

#### 2.1.3 Filtri

Allo scopo di ridurre l'interferenza con sorgenti di luminosità terze, rendendo stabile il SDVA rispetto alla luminosità dell'ambiente, si doteranno le telecamere di filtri centrati su  $\lambda$  pari a 850 nm, come i BN850-27 della MIDWEST OPTICAL, che ha una trasmissione a 850 nm superiore all'85%, come risulta dalla caratteristica riportata in.Figura 6

Figura 6. Caratteristica "Trasmissione= $f(\lambda)$ " del filtro BN850-27.

# 3. Progettazione di un set up di calcolo basato su hardware configurabile

In base alle considerazioni fatte nei punti A e B, viene definita l'architettura del SDVA e viene individuato il flow chart concettuale dell'algoritmo di visione.

#### 3.1 Architettura del Sistema Di Visione Artificiale

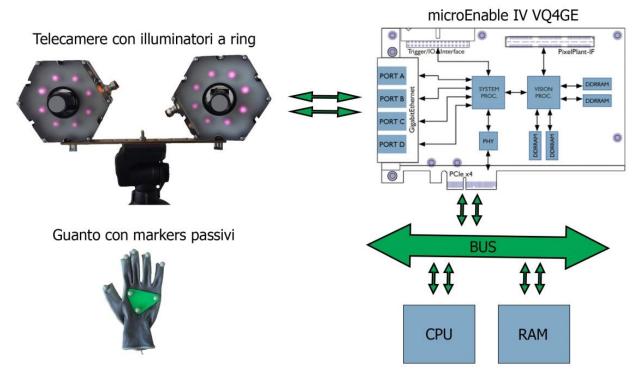

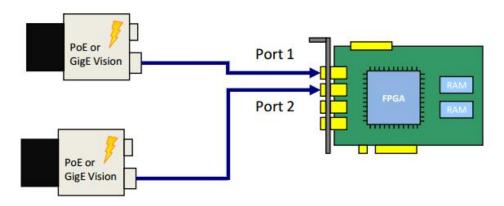

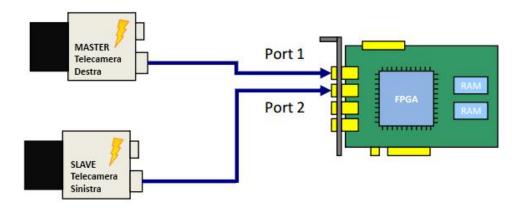

Il SDVA prevede un hardware composto da una coppia di telecamere stereo GigE, munite ciascuna di un illuminatore IR ad anello, connesse alla scheda microEnable IV VQ4GE mediante le porte GigabitEthernet. Sul frame grabber è presente un FPGA programmabile (Spartan3 FPGA XC3S4000) che effettuerà una parte dell'elaborazione a bordo della scheda. Il frame grabber è collegato ad un PC Desktop tramite PCIe x4.

La Figura 7 mostra una rappresentazione grafica dell'architettura descritta.

Figura 7. Architettura del SDVA (Sensore Di Visione Artificiale).

#### 3.2 Flow chart concettuale dell'algoritmo di visione

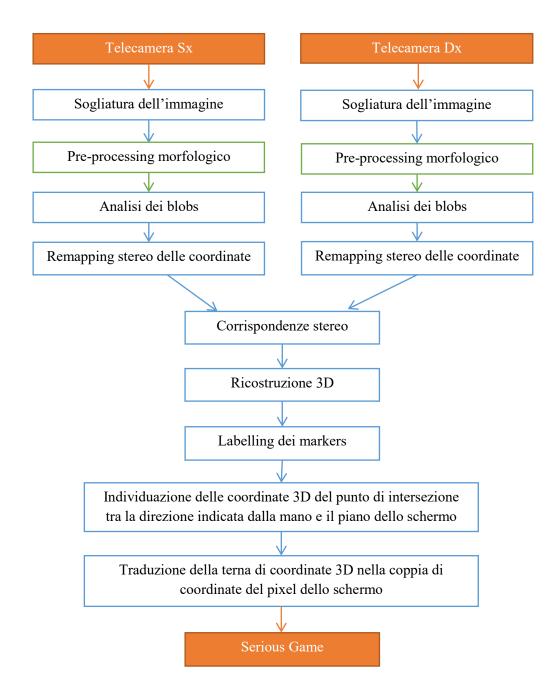

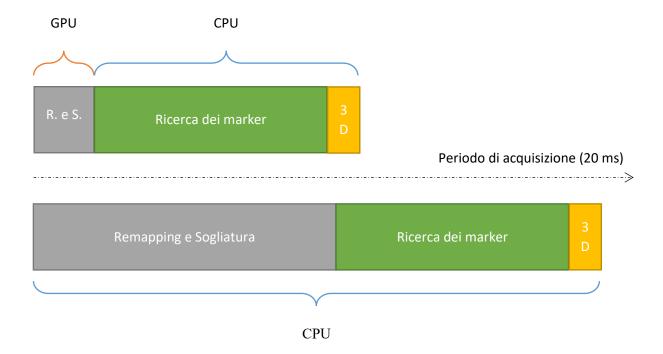

I dati provenienti dalle videocamere vengono in prima battuta processati dall'FPGA opportunamente programmato, per poi essere riversati in RAM. Un'applicazione software elabora ulteriormente questi dati al fine di ottenere le informazioni utili per il serious game.

In Figura 8 viene mostrato il flow chart concettuale dell'algoritmo di visione.

Come già anticipato precedentemente, per ridurre l'operazione di segmentazione dei markers ad una semplice sogliatura, è necessario aumentare il contrasto tra marcatore e sfondo, perciò sarà fondamentale impostare opportunamente l'otturatore delle telecamere e il loro tempo di esposizione in modo tale che nella scena siano visibili solo i marcatori passivi.

È importante sottolineare che la velocità del processo di analisi dei blob non è fissa e dipende dal contenuto dell'immagine e potrebbe rallentare l'applicazione se le immagini in ingresso sono molto rumorose. La riduzione di velocità dovrebbe essere limitata e irrilevante nelle applicazioni reali, tuttavia se si presenterà tale problema, sarà opportuno introdurre un blocco di pre-processing per velocizzare tale operazione.

Per la ricostruzione 3D delle coordinate dei markers è necessario risolvere il problema delle corrispondenze stereo, per semplificare tale problema è possibile rendere le linee epipolari delle due immagini parallele (le telecamere vengono ruotate virtualmente per rendere complanari i loro piani immagine). A tal fine è quindi necessario effettuare un remapping delle immagini provenienti dalle telecamere, poiché la struttura dell'FPGA non si presta particolarmente a tale scopo si è deciso di modificare il flusso dell'algoritmo e "rettificare" solo le coordinate 2D dei markers invece che l'intera immagine.

Figura 8. Flow chart concettuale dell'algoritmo di visione.

# 4. Implementazione del set up individuato nel capitolo 3 sulla piattaforma individuata nel capitolo 1

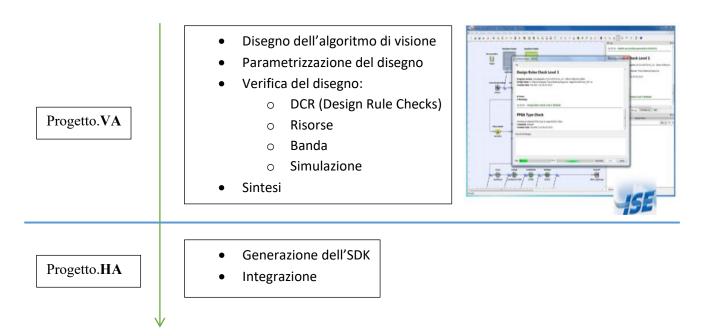

Come anticipato nel capitolo 1, la scheda microEnable IV VQ4GE appartiene alla serie V dei frame grabber della Silicon Software, e consente di programmare l'FPGA mediante il software Visual Applet. Questo tool mappa gli algoritmi di elaborazione dell'immagine come un flow charts grafico e mette a disposizione un'estesa libreria di operatori. Consente inoltre, prima della sintesi del progetto, una simulazione dei risultati visuali, con la precisione del bit, in ogni punto del modello del flusso dati. Il tool di sintesi dell'FPGA è integrato in Visual Applet e produce una applet hardware che andrà poi scaricata sulla scheda microEnable IV VQ4GE.

In **Errore. L'origine riferimento non è stata trovata.** viene mostrato il flusso di lavoro relativo all'implementazione dell'algoritmo di visione sulla scheda FPGA.

Figura 9. Diagramma a blocchi del flusso di lavoro.

#### 4.1 Mappatura hardware dell'algoritmo di visione

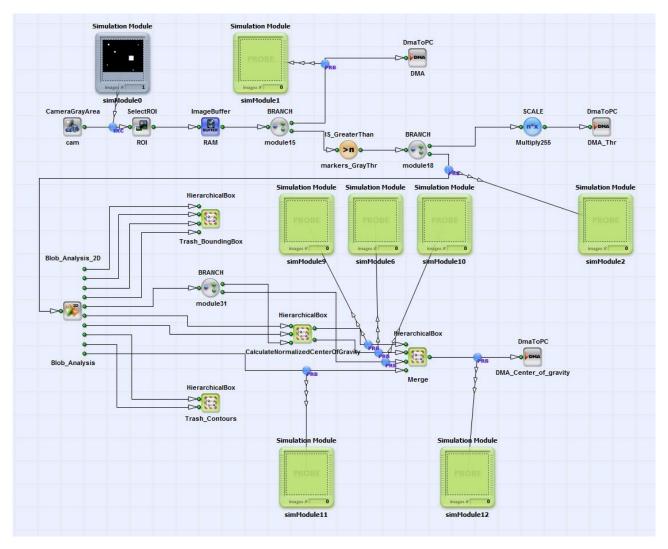

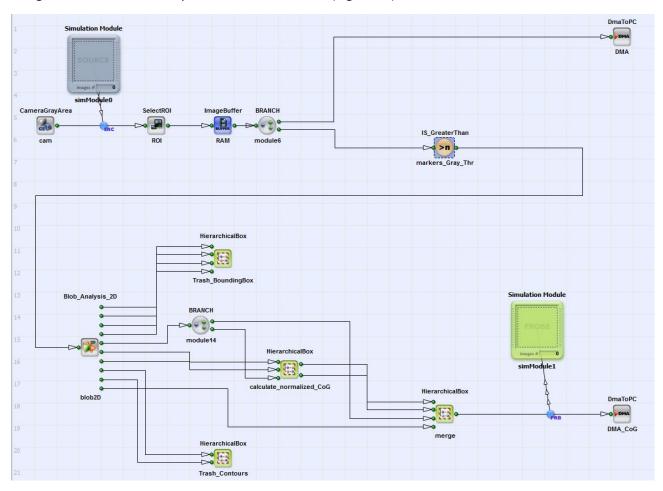

Poiché la prima parte dell'elaborazione è identica sulle due immagini stereo, l'applet è stata strutturata in due processi identici. La Figura 11 mostra come l'algoritmo di visione è stato mappato in hardware per uno dei processi.

Il disegno è stato realizzato tenendo conto che le telecamere da utilizzare per il SDVA sono le GO-5000-PGE, della casa costruttrice JAI (Figura 10). Tali telecamere hanno una risoluzione di 5MPixel (2560 x 2048), ma verranno configurate per operare con una ROI 1920x1080, che garantisce sia adeguata risoluzione, che un throughput di 56 fps (quindi superiore a quello di 50 fps fissato come target). Nello schematico è stato quindi necessario dimensionare il link di acquisizione tenendo conto delle dimensioni del sensore della telecamera ed introdurre un blocco per la selezione della ROI.

Figura 10. Telecamera JAI GO-5000-PGE.

L'applet disegnata effettua la sogliatura dell'immagine e l'analisi dei blob e trasferisce al PC host non solo il risultato di tale analisi (blocco DMA\_Center\_Of\_Gravity), ma anche l'immagine originale (blocco DMA) e quella sogliata (DMA\_Thr), in modo tale da rendere possibile il debug una volta che l'applet sarà caricata sull'FPGA.

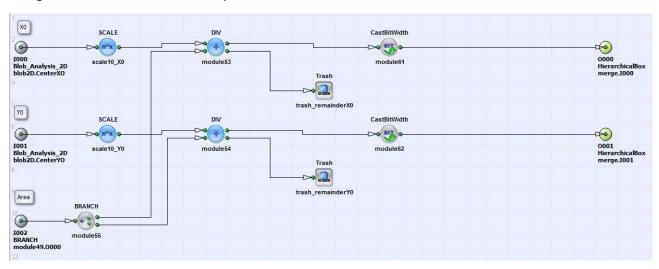

Figura 11. Progetto Visual Applet dell'algoritmo di visione relativo al Processo 0.

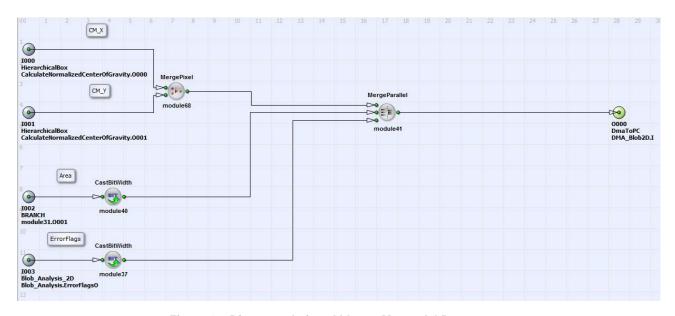

L'analisi dei blobs restituisce le coordinate dei centri di massa e le aree degli oggetti trovati nell'immagine binaria. Tali risultati vengono combinati insieme in un unico link di 32 bit con un parallelismo di 3bit. La Figura 12 mostra come i primi 32bit contengono l'informazione del centro di massa, dove la coordinata x è mappata nei 16 bit più bassi e quella y sui 16 bit più alti, i secondi 23 bit trasportano l'informazione relativa all'area dei blob e gli ultimi 32 sono relativi ai flags di errore del processo di analisi.

Per rendere l'applicazione configurabile a run time i prametri del modulo di threshold e del modulo di selezione della ROI sono stati impostati come dinamici.

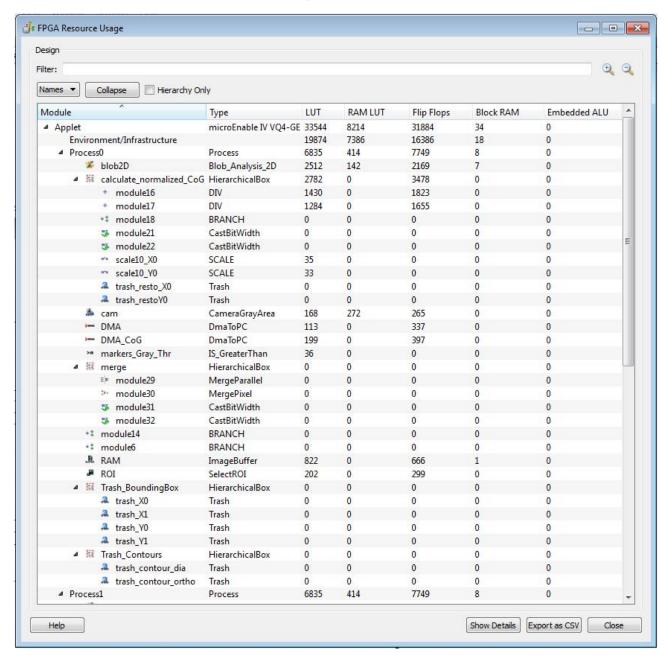

Figura 12. Disegno relativo al blocco Merge del Processo 0.

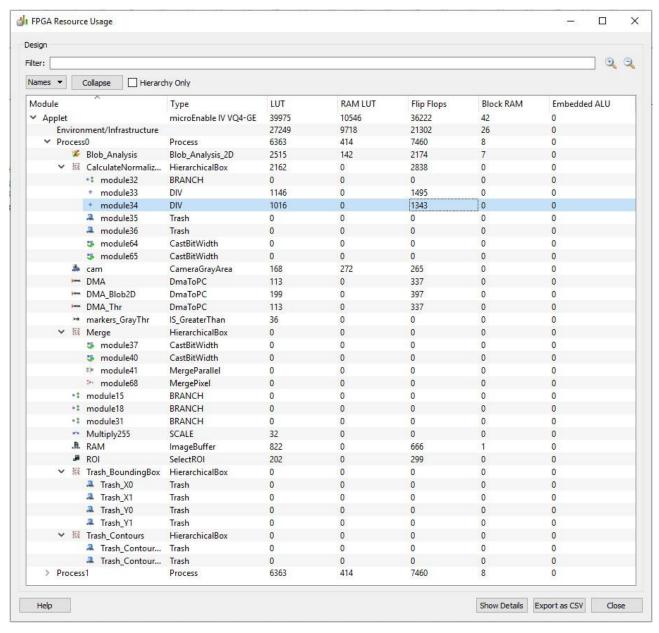

La Tabella 4 mostra come le risorse dell'FPGA a bordo del frame grabber sono sufficienti per l'implementazione dell'algoritmo di visione. In Figura 13 è possibile vedere in dettaglio le risorse utilizzate per ogni modulo del disegno. Si può osservare come i moduli più onerosi, dal punto di vista delle risorse, siano i blocchi della divisione utilizzati per normalizzare le coordinate del centro di massa. Tali blocchi però sono indispensabili per il corretto funzionamento dell'algoritmo e quindi non possono essere eliminati o sostituiti in nessun modo.

| Risorse      | Contatore | Livello di riempimento |

|--------------|-----------|------------------------|

| Blocchi RAM  | 42        | ~ 43%                  |

| LookupTables | 39975     | ~ 72%                  |

| Flip Flops   | 36222     | ~ 65%                  |

Tabella 4. Tabella sintetica dell'utilizzo delle risorse dell'FPGA

Figura 13. Risorse FPGA utilizzate dall'algoritmo di visione.

#### 4.2 Test e debug del modulo FPGA embedded

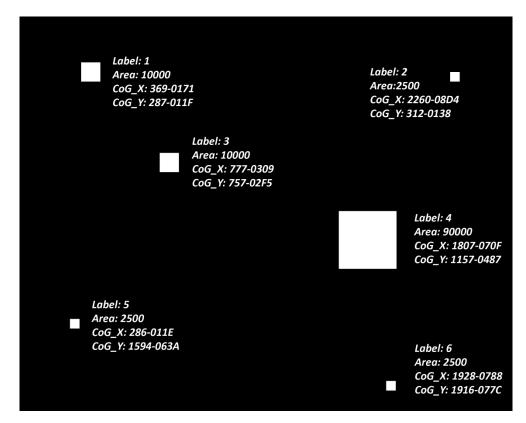

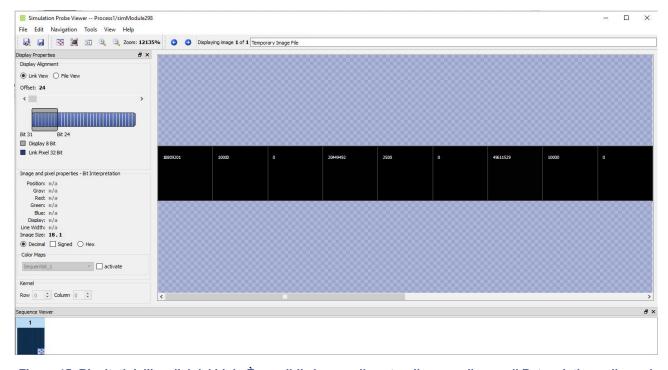

È stata effettuata un'analisi funzionale per testare il comportamento dell'implementazione. Si è utilizzata, come ingresso, l'immagine binaria di Figura 14 e mediante la sonda posta sul link del DMA\_Center\_og\_gravity (Figura 11) si è verificata la correttezza dei risultati (Figura 15).

Figura 14. Immagine binaria utilizzata per il test funzionale dell'applet.

Figura 15. Risultati dell'analisi dei blob. È possibile leggere il centro di massa, l'area e il Byte relativo agli errori dell'analisi, delle prime tre regioni dell'immagine in Figura 14.

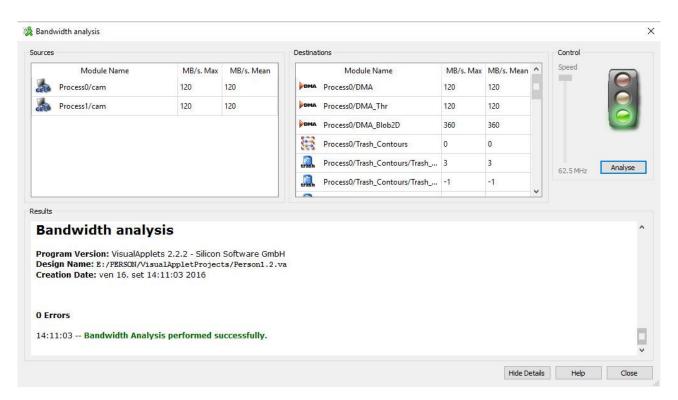

Tenendo conto che il SDVA dovrà acquisire una ROI di (1920x1080) ad un frame rate di 50 fps e che la frequenza di lavoro dell'FPGA è fissa e pari a 62.5 MHz, si è effettuata l'analisi di banda si è visto che nell'applicazione creata non ci sono colli di bottiglia (Figura 16).

Figura 16 Risultato dell'analisi di banda dell'Applet Person1.3 ottenuto impostando come ROI la dimensione massima del frame 2560\*2048

#### 4.3 Sintesi e download

Dallo stesso ambiente di Visual Applet è stato lanciato il processo di sintesi. Tale processo ha generato il file hardware binario (HAP) solo dopo aver verificato che il placement e il routing rispettassero i vincoli temporali.

Per abilitare l'algoritmo di visione sul frame grabber è necessario caricare l'applet generata sulla scheda microEnable IV VQ4GE mediante il tool MicroDisplay della Silicon Software.

# 5. Integrazione del modulo implementato con il set up di visione artificiale

Per integrare il modulo implementato nel set up di visione artificiale, è stato necessario sincronizzare le due telecamere ed implementare un interfaccia software per l'applet.

#### 5.1 Sincronizzazione delle telecamere

La sincronizzazione delle telecamere è indispensabile per una corretta ricostruzione 3D a partire da un sistema di telecamere stereo.

A tal fine si è scelto di utilizzare una telecamera come master, che acquisisce in modalità free running, e l'altra come slave, che utilizza come trigger esterno per l'acquisizione, lo stesso trigger della telecamera master.

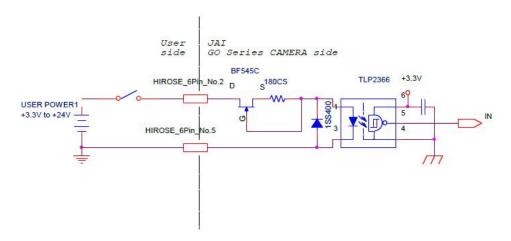

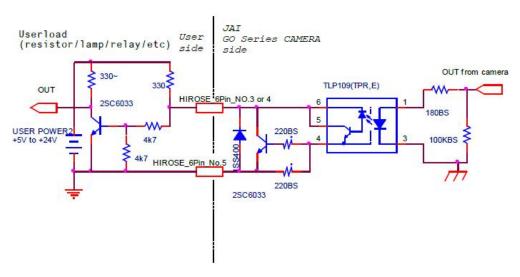

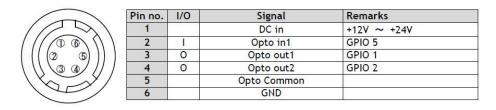

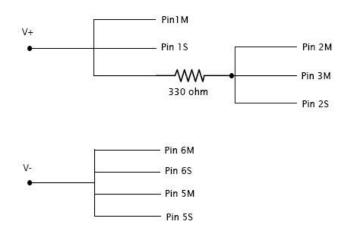

Tenendo conto dell'interfaccia ottica della telecamera JAI GO-5000-PGE (Figura 17,Figura 18), dell'assegnamento dei pin del connettore Hirose 6 (Figura 19) e dei controlli di acquisizione, è stato realizzato un circuito per la sincronizzazione della coppia di telecamere stereo. Di seguito viene illustrato sia il modulo hardware realizzato, che le impostazioni software da applicare alle due telecamere per la corretta sincronizzazione (15).

Figura 17 Diagramma della parte esterna del circuito di ingresso

Figura 18 Diagramma della parte esterna del circuito di uscita

Figura 19 Vista dall'esterno del connettore Hirose a 6 pin e tabella dell'assegnamento dei pin

#### 5.1.1 Modulo Hardware

In Figura 20 è mostrato lo schematico del circuito realizzato per l'alimentazione e la sincronizzazione della coppia di telecamere stereo. Il trigger della telecamera master (segnale Exposure Active) è messo in output, sui pin 3, ed inviato in input alla slave, sui pin 2.

Figura 20 Circuito per la sincronizzazione delle telecamere

#### 5.1.2 Impostazioni software

La Tabella 5 e la Tabella 6, mostrano come configurare la coppia di telecamere stereo per la corretta sincronizzazione.

|             | MASTER                         |                  |

|-------------|--------------------------------|------------------|

| Acquisition | Trigger Mode(Trigger Selector) | Off              |

| Controll    | Exposure Mode                  | Timed            |

|             | Exposure Time                  | et               |

|             | Frame Rate                     | fps              |

| Digital IO  | Line Selector                  | Line 1 Opt 1 Out |

| Controll    | Line Source                    | Exposure Active  |

Tabella 5 Configurazione della telecamera master

| SLAVE       |                                  |                 |  |  |  |

|-------------|----------------------------------|-----------------|--|--|--|

| Acquisition | Trigger Mode(Trigger Selector)   | On              |  |  |  |

| Controll    | Exposure Mode                    | Timed           |  |  |  |

|             | Exposure Time                    | et              |  |  |  |

|             | Trigger Source(Trigger Selector) | Line 5 OPT IN 1 |  |  |  |

Tabella 6 Configurazione della telecamera slave

#### 5.1.3 Valutazioni sul modulo di sincronizzazione implementato

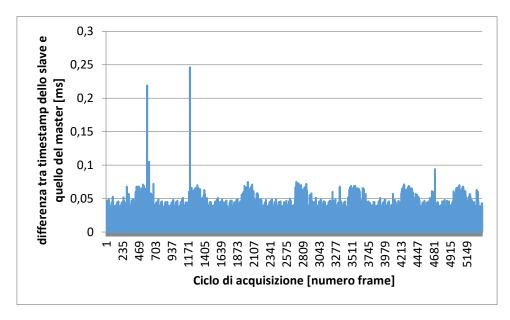

Il Grafico 1 mostra la differenza tra l'istante di acquisizione della telecamera master e quello della telecamera slave, in un ciclo di acquisizione di 1 minuto e 47 secondi. Tale differenza risulta essere in media di 0,01ms con un deviazione standard di 0,02ms. Dato che il periodo di acquisizione è di 20ms, si può considerare che i frames delle due telecamere siano stati sincronizzati correttamente.

Grafico 1 Differenza tra l'istante di acquisizione della telecamera master e della slave

#### 5.2 Interfaccia Software

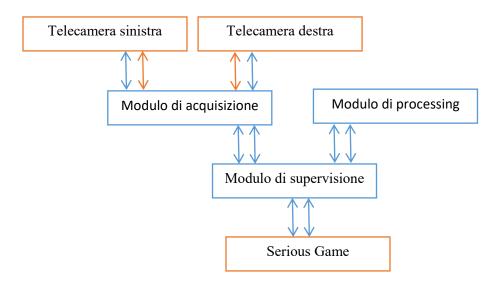

La Figura 21 descrive l'architettura del sistema di visione artificiale.

Figura 21 Componenti del Sistema Di Visione Artificiale

Per integrare l'applet Person1.3, è stato necessario sviluppare un nuovo modulo di acquisizione in grado di interfacciarsi con il frame grabber, invece che direttamente con la coppia di telecamere stereo, e con il modulo di supervisione. Anche il modulo di processing ha subito delle modifiche in quanto, invece di ricevere, come input, i frames acquisiti, riceverà direttamente le coordinate dei centri di massa dei markers.

#### 5.2.1 Modulo di acquisizione

Il modulo di acquisizione implementato, è costituito dalle classi C++:

- GbEStereo

- Blob2D

#### 5.2.1.1 Classe GbEStereo

La classe GbEStereo costituisce il cuore del modulo di acquisizione, in quanto si interfaccia sia con il frame grabber, mediante la funzioni della libreria Runtime della Silicon Software, che con il modulo di supervisione.

La Figura 22 descrive la struttura della classe GbEStereo.

```

GbEStereo

- board_number: int

- master_cam_port: int

- slave_cam_port: int

- dll_name: QString

- width: int

- height: int

- gray_thr: int

- nr of buffer: int

parameters: const QMap<QString, QVariant>

- acquiring: bool

- log_file: QFile

+ GbEStereo(board_number: const int, master_cam_port: const int, slave_cam_port: int, dll_name:

const QString, width: const int, height: const int, nr_of_buffer: const int, gray_thr: const int,

log_file_path: QString = "", parent: QObject * = 0);

+ set_parameters(parameters: const QMap<QString, QVariant>)

+ set_thread(thread: QThread*)

+ stop_acquiring()

- log(message: const QString)

SIGNALS:

+ CoG_available(master_CoG: cv::Mat &, master_timestamp: const unsigned int, slave_CoG: const

cv::Mat &, slave_timestamp: unsigned int)

SLOTS:

+ acquire()

Figura 22 Diagramma delle classi di GbEStereo

```

Per poter utilizzare il modulo di acquisizione è necessario:

- Instanziare e inizializzare un oggetto della classe GbEStereo

- Impostare i parametri di acquisizione

- Associare un thread all'oggetto instanziato

- Avviare il thread, che a sua volta avvierà l'acquisizione

- Interrompere l'acquisizione mediante il metodo stop\_acquiring()

L'inizializzazione dell'oggetto della classe GbEStereo avviene passando al costruttore i seguenti parametri:

- board number: indice del frame grabber da cui effettuare l'acquisizione

- master cam port: indice della porta GigE della telecamera master

- slave\_cam\_port: indice della porta GigE della telecamera slave

- dll name: nome dell'applet da caricare sul frame grabber ("Person1.3")

- width: larghezza del frame da acquisire

- height: altezza del frame da acquisire

- gray\_thr: levello di grigio con cui sogliare l'immagine

- nr\_of\_buffer: dimensione del buffer circolare di immagini

Gli unici parametri dell'acquisizione che sarà necessario impostare sono:

- il frame rate

- il tempo di esposizione

Questi parametri vanno invece impostati con il metodo set\_parameters(const QMap<QString, QVariant> parameters).

Ogni volta che una coppia di immagini stereo viene acquisita e le coordinate dei markers vengono calcolati, l'oggetto della classe GbEStereo emette il segnale CoG\_available, passando come parametri:

- un reference alla matrice delle coordinate dei markers della telecamera master (master\_CoG)

- il time stamp, in microsecondi, corrispondente al frame acquisito della telecamera master (master timestamp)

- un reference alla matrice delle coordinate dei markers della telecamera slave (slave\_CoG)

- il time stamp, in microsecondi, corrispondente al frame acquisito della telecamera slave (slave\_timestamp)

Di seguito viene mostrato il codice di esempio per l'utilizzo del modulo di acquisizione:

```

//! Instanzia e inizializza un oggetto della classe GbEStereo

GbEStereo gbe stereo (0, PORT A, PORT B, "Person1 3.hap", 1920, 1080, 16, 80,

"log gbestereo.txt" );

//! Instanzia un thread da associare all'oggetto gbe stereo

QThread gbe stereo thread;

//! Imposta i parametri di acquisizione

QMap<QString, QVariant> parameters;

parameters["AcquisitionFrameRate"] = 56;

parameters["ExposureTime"] = 1 * 1e+3;

gbe stereo.set parameters( parameters);

//! Associa il thread all'oggetto GbEStereo

gbe stereo.set thread( &gbe stereo thread );

gbe stereo.moveToThread( &gbe stereo thread );

//! Avvia l'acquisizione

gbe stereo thread.start( QThread::TimeCriticalPriority );

//! Interrompe l'acquisizione

gbe stereo.stop acquiring();

```

#### 5.2.1.2 Classe Blob2D

La classe Blob2D, è invece utilizzata dalla classe GbEStereo, per la lettura dei risultati dell'analisi dei blob.

La struttura della classe è mostrata in Figura 23.

```

- m_noOfObjects: unsigned int

- m_Features: BlobStruct*

- CoG_vect: cv::Mat

+ ReadRawData(p_blobData: unsigned char*, p_noOfObjects: unsigned int): int

+ GetNumberOfObjects(): unsigned int

+ GetArea(objectIndex: unsigned int): unsigned int

+ GetCoGX(objectIndex: unsigned int): double

+ GetCoGY(objectIndex: unsigned int): double

+ GetErrorflags(objectIndex: unsigned int): unsigned int

+ get_CoG_vect():cv::Mat

```

Figura 23 Diagramma delle classi di Blob2D

Gli attributi privati sono i seguenti:

- m noOfObjects: numero delle regioni trovate nell'immagine

- m Features: vettore di elementi BlobStruct, che memorizzano i risultati dell'analisi dei blob

- CoG vect: matrice 1xN, contenente i centri di massa di tutte le regioni dell'immagine

L'elemento BlobStruct contenete i risultati dell'analisi dei blob relativi ad una singola regione, ed in particolare:

- L'area (Area)

- La coordinata x del centro di massa (CoGX)

- La coordinata y del centro di massa (CoGY)

- Il byte (Errorflags) relativo ai flags di errore, che indicano se si è verificato un overflow del numero di blob¹

La lettura dei risultati della blob analisi viene effettuata mediante il metodo ReadRowData, al quale è necessario passare:

- Il puntatore al buffer di memoria dei risultati della blob analisi (p\_blobData)

- Il numero di regioni che sono state trovate nell'immagine (p noOfObjects)

La classe Blob2D, mette inoltre a disposizione una serie di funzioni in grado di restituire, per ciascuna regione, l'area e il centro di massa.

Il metodo get\_CoG\_vect() restituisce invece una matrice 1xN, dove N è pari al numero di regioni trovate nell'immagine. Ciascun elemento della matrice è un vettore di due double, contenente la coordinata x e la coordinata y del centro di massa.

Di seguito viene mostrato un frammento di codice della classe GbEStereo in cui vengono utilizzati due oggetti della classe Blob2D:

```

//! Recupera i risultati della blob analisi della telecamera master

Blob2D blob master;

unsigned char* iPtr CoG master = (unsigned char*) Fg getImagePtrEx(fg,

last_CoG_nr_master, 1, p_mem_CoG_master);

int DMAlength CoG master = last CoG nr master;

Fq getParameter (fg, FG TRANSFER LEN, &DMAlength CoG master, 1);

//! Legge i risultati della blob analisi dal buffer

blob master.ReadRawData(iPtr CoG master, DMAlength CoG master / 12); //12

Bytes per Object

//! Recupera i risultati della blob analisi della telecamera slave

Blob2D blob slave;

unsigned char* iPtr CoG slave = (unsigned char*) Fg getImagePtrEx(fg,

last_CoG_nr_slave, 3, p_mem_CoG_slave);

int DMAlength CoG slave = last CoG nr slave;

g getParameter (fg, FG TRANSFER LEN, &DMAlength CoG slave, 3);

//! Legge i risultati della blob analisi dal buffer

blob slave.ReadRawData(iPtr CoG slave, DMAlength CoG slave / 12); //12 Bytes

per Object

```

#### 5.2.2 Modulo di processing

<sup>&</sup>lt;sup>1</sup> 128 è il numero massimo di blobs impostato nell'Applet Person 1.3

In questa nuova struttura del SDVA, il modulo di processing è stato notevolmente snellito, in quanto una tra le operazioni più onerose dal punto di vista computazionale, il calcolo dei centri di massa delle regioni, è stato spostato sulla piattaforma FPGA.

Il modulo di processing, invece di processare le immagini acquisite, si ritrova a dover processare solo le coordinate dei markers della scena. Questo implica un'ulteriore velocizzazione del sistema, in quanto l'operazione di remapping sulle coordinate dei 16 markers (8 markers per ciascun²), è molto meno onerosa rispetto al remapping dei frames sinistro e destro, ciascuno costituito da 2 MPixels³.

#### 6 Test e debug del sistema integrato

Il sistema integrato di parte hardware ed interfaccia software è stato testato e ha rivelato dei problemi di instabilità del pixel selezionato, nella fase di puntamento dello schermo. Tale problema è stato risolto andando ad apportare una modifica al progetto della parte hardware del SDVA. La nuova versione del sistema è stato testata e sono state valutate le prestazioni dal punto di vista computazionale.

#### 6.1 Problema dell'instabilità del puntamento

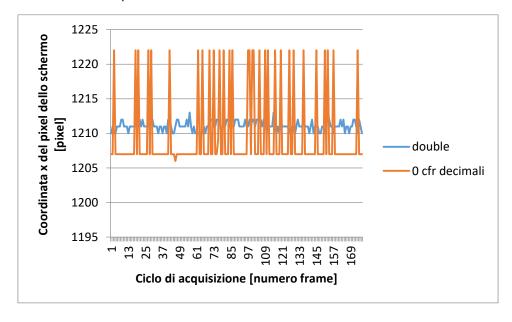

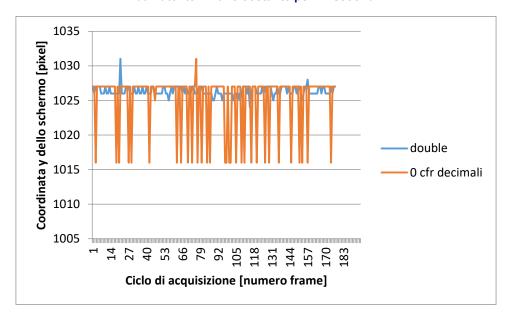

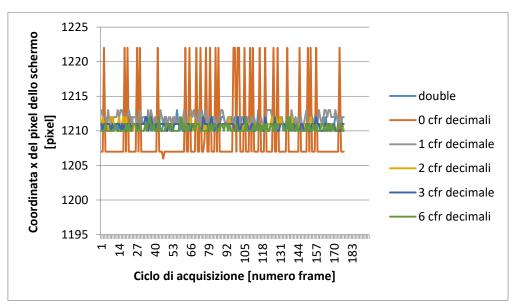

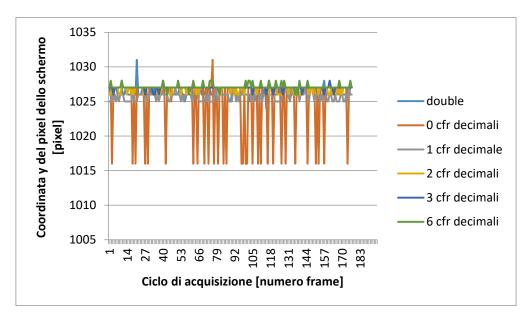

Indicando un punto fisso sullo schermo, per un intervallo di tempo, il punto del monitor che il SDVA andava a selezionare non era costante nell'intero periodo, ma oscillava attorno ad un punto medio fisso. Si è ipotizzato che tale problema fosse legato al fatto che il calcolo dei centri di massa dei markers, effettuato sulla scheda FPGA, restituisse un intero e non un double, come nel caso del SDVA sviluppato per lavorare esclusivamente con la CPU e la GPU. Per verificare la validità di tale ipotesi, è stato modificato il modulo di processing del SDVA, pensato per lavorare senza frame grabber, in modo tale che arrotondasse all'intero i valori dei centri di massa dei markers. Si è riscontrato che, con questa modifica, si verificava lo stesso tipo di variabilità del pixel puntato. Il Grafico 2 e il Grafico 3 mostrano i risultati di tale test. Come è possibile osservare, nel caso di troncamento all'intero dei centri di massa, la propagazione di tale errore al calcolo del pixel puntato è notevole, in quanto si hanno delle oscillazioni che arrivano fino a differenze di 16 pixel tra due frames consecutivi, mentre nel caso in cui non viene fatto nessun troncamento si può avere al massimo una variazione di 2-3 pixels.

<sup>&</sup>lt;sup>2</sup> Il modello di mano scelto, per il SDVA, prevede 8 markers

\_

<sup>&</sup>lt;sup>3</sup> La ROI di acquisizione dell'SDVA è di 1920x1080

Grafico 2 Grafico della coordinata x del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi

Grafico 3 Grafico della coordinata y del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi

Per capire il numero di cifre decimali sufficienti ad eliminare il problema dell'instabilità del puntamento, è stato effettuato un ulteriore test, sfruttando sempre il modulo di processing del SDVA pensato per lavorare senza frame grabber. Il Grafico 4e il Grafico 5 mostrano i risultati di tale test.

Grafico 4 Grafico della coordinata x del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi. Relativo al troncamento dei centri di massa dei markers rispettivamente a 0, 1, 2, 3 e 6 cifre decimali

Grafico 5 Grafico della coordinata y del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi. Relativo al troncamento dei centri di massa dei markers rispettivamente a 0, 1, 2, 3 e 6 cifre decimali

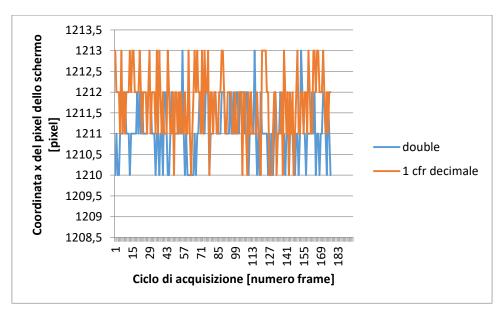

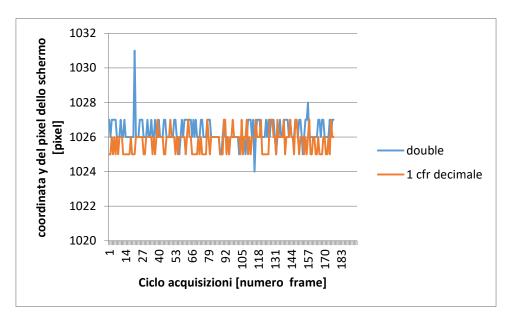

Come è possibile osservare più chiaramente nel Grafico 6 e nel Grafico 7 un troncamento alla prima cifra decimale è sufficiente ad eliminare il problema dell'instabilità del puntamento, dovuta alla propagazione dell'errore.

Grafico 6 Grafico della coordinata x del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi. Relativo al troncamento a 0 cifre decimali dei centri di massa dei markers

Grafico 7 Grafico della coordinata y del pixel selezionato dal SDVA al variare del tempo, mentre il pixel puntato dall'utente rimane costante per 24 secondi. Relativo al troncamento a 0 cifre decimali dei centri di massa dei markers

#### 6.2 Soluzione all'instabilità del puntamento

Come abbiamo visto, per risolvere il problema dell'instabilità del pixel puntato è sufficiente troncare il centro di massa del pixel alla prima cifra decimale. Ciò semplifica notevolmente le modifiche da apportare al progetto hardware e software, in quanto la struttura del link dei risultati dell'analisi dei blob, rimane invariata. Infatti, tenendo conto che la ROI di acquisizione è 1920x1080 e che vogliamo approssimare alla prima cifra decimale, per la codifica delle coordinate dei centri di massa, sono ancora sufficienti 16 bit.

La Figura 24 mostra il nuovo blocco per la normalizzazione delle coordinate dei centri di massa.

Figura 24 Disegno relativo al blocco calculate\_normalized\_CoG

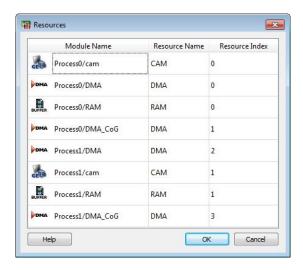

Questa modifica però, porta ad un aumento delle risorse FPGA necessarie, come è possibile vedere nella Tabella 7. Più si ampliano le risorse richieste più critica diventa la fase di sintesi del progetto, ed in particolare il placement, il routing e il check del rispetto dei vincoli di tempo. Per ridurre tale criticità, e visto che una fase di test è già stata effettuata, si è ridotto il numero di DMA utilizzati dall'applet. Si è preferito lasciare il DMA relativo alle immagini acquisite per garantire un minimo debug, ma si è eliminato il

DMA relativo al risultato della sogliatura del frame acquisito. La Tabella 8 mostra le risorse utilizzate nel caso di questa nuova applet, "Person1.6", che utilizza solo 4 DMA.

| Risorse      | Contatore | Livello di riempimento |

|--------------|-----------|------------------------|

| Blocchi RAM  | 42        | ~ 43%                  |

| LookupTables | 41215     | ~ 74%                  |

| Flip Flops   | 37666     | ~ 68%                  |

Tabella 7 Tabella sintetica dell'utilizzo delle risorse dell'FPGA nel progetto che prevede 6 DMA

| Risorse      | Contatore | Livello di riempimento |

|--------------|-----------|------------------------|

| Blocchi RAM  | 34        | ~ 35%                  |

| LookupTables | 33544     | ~ 60%                  |

| Flip Flops   | 31884     | ~ 57%                  |

Tabella 8 Tabella sintetica dell'utilizzo delle risorse dell'FPGA nel progetto che prevede 4 DMA

In Figura 25 è possibile vedere le schematico del Processo 0 relativo alla nuova applet Person1.6. Il blocco merge, come abbiamo anticipato, è rimasto invariato (Figura 12).

Figura 25 Progetto Visual Applet dell'algoritmo di visione relativo al Processo 0

La Tabella 9 mostra la corrispondenza tra i moduli del progetto e le risorse dell'FPGA, mentre la Figura 26 descrive in dettaglio le risorse FPGA utilizzate da ciascun singolo modulo.

Tabella 9 Tabella degli indici delle risorse utilizzate

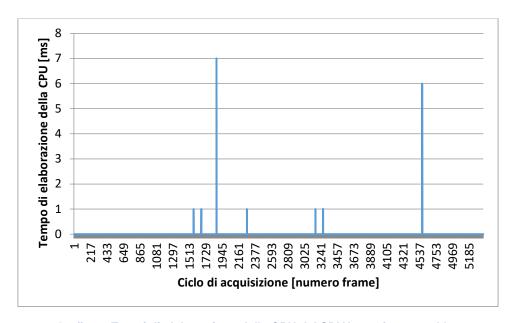

Figura 26 Risorse FPGA utilizzate dall'applet Person1.6